News:

- Nanoarch 2017 will be held in Newport, RI, United States. Click here for NANOARCH 2017.

- IEEE Transaction on Nanotechnology seeks original research manuscripts for a Special Issue on Revolutionary 3-D Integration and Design for Next Generation Computing. Please see Call for Papers here

- IEEE Transaction on Multi-Scale Computing Systems seeks original research manuscripts for a Special Issue on Cognitive Computing with Emerging Technology. Please see Call for Papers here

- NANOARCH 2016 Awards

Best Paper Award: Erya Deng, Guillaume Prenat, Lorena Anghel and Weisheng Zhao, "Multi-context Non-volatile Content Addressable Memory Using Magnetic Tunnel Junctions"

Best Student Paper Award: Jintao Yu, Razvan Nane, Muhammad Adib Bin Haron, Said Hamdioui, Henk Corporaal and Koen Bertels, "Skeleton-Based Design and Simulation Flow for Computation-In-Memory Architectures"

Best Concept Paper Award: Navneet Gupta, Adam Makosiej, Andrei Vladimirescu, Amara Amara, Sorin Cotofana and Costin Anghel, "TFET NDR Skewed Inverter based Sensing Method" - IEEE Transaction on Multi-Scale Computing Systems seeks original research manuscripts for a Special Issue on Cognitive Computing with Emerging Technology. Please see Call for Papers here

For visa support letters, please send a request to supportletters@acm.org with the information below (please note all fields marked with * are required). Those requesting a letter should allow up to one week to receive it.

- Name*: (as it appears on attendee passport) and mailing address

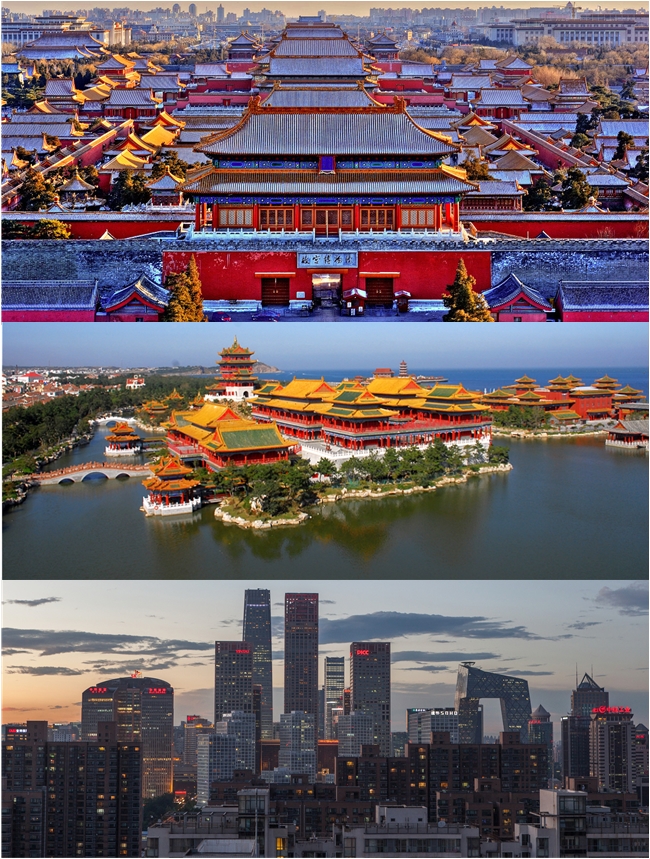

- Conference*: 12th ACM/IEEE International Symposium on Nanoscale Architectures (Nanoarch 2016), Beijing, China

- Attendee registration confirmation number*

- Authors/Speakers can provide the title of their talk

- Fax number or email address of where letter can be sent*.

NANOARCH 2016 is the leading conference on post-CMOS nanocircuits, nanoarchitectures, emerging nanoscale CMOS, and nanoscale fabrics in general. Both experimental and theoretical works are sought after.

NANOARCH is the annual cross-disciplinary forum for the discussion of novel post-CMOS nanocomputing directions and emerging nanoscale CMOS. The symposium seeks papers on innovative ideas for solutions to the principal challenge facing integrated electronics in the 21st century - how to design, fabricate, and integrate nanosystems to overcome the fundamental limitations of CMOS. In particular, such systems could (1) contain unconventional nanodevices with unique capabilities, including directions beyond simple switches, (2) introduce new logic and memory concepts, (3) involve novel circuit styles, (4) introduce new concepts for computing, (5) reconfigure and/or mask faults at much higher rates than in CMOS, (6) explore security architectures with nanotechnology, (7) involve new paradigms for manufacturing, and (8) rethink the methodologies and design tools involved.

NANOARCH is the annual cross-disciplinary forum for the discussion of novel post-CMOS nanocomputing directions and emerging nanoscale CMOS. The symposium seeks papers on innovative ideas for solutions to the principal challenge facing integrated electronics in the 21st century - how to design, fabricate, and integrate nanosystems to overcome the fundamental limitations of CMOS. In particular, such systems could (1) contain unconventional nanodevices with unique capabilities, including directions beyond simple switches, (2) introduce new logic and memory concepts, (3) involve novel circuit styles, (4) introduce new concepts for computing, (5) reconfigure and/or mask faults at much higher rates than in CMOS, (6) explore security architectures with nanotechnology, (7) involve new paradigms for manufacturing, and (8) rethink the methodologies and design tools involved.

This symposium includes several exciting sessions and opportunities for interaction. In addition to Regular papers presenting original techniques / directions, it invites the community to also submit Nanofabric Progress Updates giving a progress update of their nanofabrics directions to date across devices, circuits, architecture and manufacturability aspects - e.g. 2D/3D nanowire, magnonic, memristor, CNT, graphene, FinFETs, and QCA based directions.

In addition, Concept papers are invited from the broader nanotechnology community to highlight promising nanomaterial, nanodevice, nanomanufacturing, and integration ideas with application potential in nanoscale architectures.

Example topics (both theoretical and experimental) of interest include (but are not limited to):

- Novel nanodevices and manufacturing/integration ideas with a focus on nanoarchitectures

- Nanoelectronic circuits, nanofabrics, computing paradigms and nanoarchitectures

- 2D/3D/hybrid nanodevice integration and manufacturing, with variability, defect and fault tolerance

- Nanodevice and nanocircuit models, methodologies and computer aided design tools

- Fundamental limits of computing at the nanoscale

Authors are invited to submit papers of 6 pages in length for the Regular, nano CMOS, Reliability, Nanofabrics Progress Updates, and 2 pages in length for Concept Sessions. We sincerely hope you can participate in NANOARCH 2016. Should you have any questions, please contact us using the links to the left.